Modeling Basic Gates through Verilog

Modeling Basic Gates through Verilog: Logic gates are an essential unit of digital electronics. They are usually constructed in LSI and VLSI circuit along with other devices. The name logic gate is derived from the ability of such devices to make a decision. Likewise, it produces outputs for different combinations of the applied input.

Classification of Gates

The input and output of logic gates can occur only in two levels as HIGH and LOW, MARK and SPACE, TRUE and FALSE, ON and OFF, or simply zero and one. The function of each logic gate will be represented by a Boolean expression. Furthermore, the truth table is a means of describing how a logic circuit output depends on the logic level present in the circuit’s input. The number of output combinations will be 2^N for the “N-input” truth table. In digital electronics, there is a total of 7 logic gates with the help of which we can design any digital circuit. These are classified as:

Basic Gate

- NOT

- AND

- OR

- Universal Gates

- NAND

- NOR

- Special Purpose Gates

- EX-OR

- EX-NOR

Introduction to Verilog

Verilog is a Hardware description language that has evolved to create a synthesizable model of digital as well as analog designs. Similarly, the constructs for verification of digital design can also be developed in Verilog. It is analogous to C programming language. However, it has few differences, too, like Instantiation, Concurrency, Timing, etc. Verilog allows a different level of abstraction, and these abstractions can also be mixed in a single model. Therefore, a design can be represented as switches, gates, RTL, or behavioral codes.

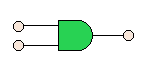

AND Gate

The AND gate can have two or more inputs but only one output. The logical symbol and truth table is below. Also, the logical expression is C= A.B, where ‘.’ is binary multiplication. Hence, it is clear from the truth table below that if all the inputs or any of the data is LOW the output is also at logic zero. However, the output is HIGH only when all the inputs are one. The AND operation is performed exactly like ordinary multiplication of binary digits.

| Input a | Input b | Output c |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Due to disposition of this hardware description language, we can represent a design in various levels of abstraction namely Switch-level, Gate-Level, Data-flow, and Behavioral. In other words, Switch level provides the lowest level of abstraction and Behavioural is on the other end.

Design Module

Modeling Basic Gates through Verilog: Gate level modeling is used when we want to know the construction of the design in term gates. Gates are primitive in Verilog therefore the functionality of gates is already declared. For that reason, Gate level modeling is used when we want to know the primitive construction of the design.

//Gate-Level Modeling

module andgate(c,a,b); //module declaration

input a,b; //default data type is wire. Wire represents continuous signal

flow.

output reg c; // reg is meant for storage

and a1(c,a,b); // calling the declared functionality in Verilog

endmodule //module terminationThe operation is performed between a and b, and the result is passed to output c. Similarly, we can design the same Gate by Data- Flow modeling. As the name suggests, this modeling specifies the flow of data. Certainly, the abstraction will be more in the respective modeling style because it is styled according to the Boolean expression. It a continuous type of assignment and therefore executes in parallel.

//Data-Flow Modeling

module andgate(c,a,b);

input a,b;

output reg c;

assign c=a & b; // it depends on the logical expression

endmoduleThe highest level of abstraction is provided by behavioral modeling. It is a procedural type assignment. In other words, the functional block will execute when inputs change. The keyword is always @(). @() is called the sensitivity list and contains the list of variables whose modulation will trigger the execution. (*) can be used instead. It is equivalent to all the variables written in the sensitivity list.

//Behavior Modeling

module andgate(c,a,b);

input a,b;

output reg c;

always@ (*) // can be replaced by always@ (a or b) or always @(a,b)

begin // begin and end are like parenthesis in C programming language

if(a==1 && b==1) // these case statements reflect the behavior of the truth

begin table of Gate.If-else statement is same as C language.

c=1;

end

else // it is not necessary to put begin-end block here.

c=0;

end

endmoduleTest Bench

Test bench or test harness is a piece of code required for the design verification. First of all, we will transfer the signal between the test bench and the design block. A sequence of inputs is applied after a time delay, and if the required output is displayed, as the resulting design is verified.

module andgate_tb; // list of ports can be ignored if no signals are

exchanged with environment

wire t_c; // According to syntax, output has wire data type in test bench

reg t_a,t_b; //data type of input is reg

andgate dut ( t_c, t_a, t_b); //Instantiation

initial //initial is also a procedural assignment ,but used in test harness

only

begin

$monitor(t_a, t_b,t_c); //function to moniter the change in variables

t_a = 0; // first set of input

t_b = 0;

#50 //delay

t_a = 0;// second set of inputs

t_b = 1;

#50

t_a = 1;

t_b = 0;

#50

t_a = 1;

t_b = 1;

end

initial

begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule // module terminationThe module is the basic building block in Verilog and it is followed by a module name, which is andgate in our case. The module takes the list of ports as its argument. Furthermore, the use of an initial block is on the user. It can be used with a single function or with a group of tasks or inputs.

For instance, initial

$moniter( ); // It is single function so we do not need to put begin-end block

The other example is

Initial

begin //while clubbing together, we need to put begin end block

$moniter();

$dumpfile(“dump.vcd”);

$dumpvars;

end

Instantiation is creating a copy of the module with its unique port names. As a result, we bring a copy of the module into the test bench. A module can be instantiated directly, as we did in the above example. Similarly, it can be instantiated implicitly, as we will do in the AND gate’s test bench.

Module_name design_under_test_name();

In the argument list, we give the test bench’s port because we wish to connect with the design module’s port. The order of the test bench’s port should be identical to that of design. Moreover, it is a bad practice to leave any port unconnected.

Function $dumpfile(“dump.vcd”); tells which file needs to be dumped to generate the waveform and $dumpvars tells variable to be monitored.

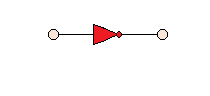

NOT Gate

The NOT has a single input and single output variable. The NOT operation is also referred to as ‘INVERSION’ or ‘COMPLEMENTATION.’ Thus, its output logic level is always the opposite of its input logic level. The expression is B=~A. The below figure and table shows the logic symbol and truth table of Inverter, respectively.

| Input a | Output b |

| 0 | 1 |

| 1 | 0 |

When an even number of NOT gates/inverters are connected in feedback, it acts like a bistable multivibrator (essential memory element). The even number of NOT gates/inverters without feedback act like a buffer. Additionally, buffers are used to increase the driving capacity of a gate. Similarly, an odd number of NOT gates/inverters connected in feedback act like an astable multivibrator or a square wave generator, or a clock pulse generator or, a free-running oscillator.

Design Module

// Gate-Level Modeling

module inverter(b,a); // defining the top level module

input a;// defining input

output reg b;// defining output

inverter i1(b,a);

endmodule // module termination//Data-Flow Modeling

module inverter(output b,input a); // input and outputs can also be defined here

assign b= ~a; //logical expression

endmodule // module termination//Behavioral Modeling

module inverter (b,a);

input a;

output reg b;

always @ (*)

begin

if(a==0) // behavior of test bench

begin

b=1;

end

else

b=0;

end

endmoduleTest Bench

module inverter_tb;

wire t_b;

reg t_a;

inverter dut ( .a(t_a), .b(t_b));

initial

begin

$monitor(t_a, t_b);

t_a = 0;

#50

t_a = 1;

#100

t_a = 0;

#50

t_a = 1;

end

initial

begin

$dumpfile("dump.vcd");

$dumpvars;

End

endmodule

inverter dut ( .a(t_a), .b(t_b));

Here, we have use implicit instantiation, which is independent of the order. The syntax is (.)port of the design module( port of test bench).

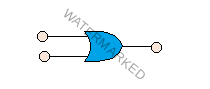

OR Gate

The OR gate can have two or more inputs but only one output. The logic symbol and the truth table for the OR gate are shown. Thus, the logical expression is C= A+B. It is clear from the truth table that if all the inputs or any of the data is High, the output is HIGH. Whereas if all the inputs are LOW, then the output is low. OR gate is binary addition of two bits.

| Input a | Input b | Output c |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Design Module

//Gate Level Modeling

module orgate(c,a,b);

input a,b;

output reg c;

or a1(c,a,b); // calling functionality

endmodule//Data-flow Modeling

module orgate(c,a,b);

input a,b;

output reg c;

assign c= a | b; // logical expression

endmodule//Behavioral Modeling

module orgate(c,a,b);

input a,b;

output reg c;

always @ (*)

begin

if(a==0 && b==0) // behavior of test harness

begin

c=0;

end

else

c=1;

endmoduleTest Bench

module orgate_tb;

wire t_c;

reg t_a,t_b;

orgate dut(.c(t_c), .a(t_a), .b(t_b));

initial

begin

$monitor(t_a, t_b, t_c);

t_a=0;

t_b=0;

#100

t_a=0;

t_b=1;

#100

t_a=1;

t_b=0;

#100

t_a=1;

t_b=1;

end

initial

begin

$dumpfile ("orgate.vcd");

$dumpvars;

end

endmodule

Conclusion

So, in this article “Modeling Basic Gates through Verilog“, we have modeled the basic gates using Verilog HDL. Verilog is similar to the C programming language, but at the same time, has noticeable differences too. Therefore, to master the art of designing and verification, one should have a strong foundation in both C language and digital electronics. Modeling is upon the designer’s discretion and level of abstraction needed, but the essence will remain the same. In the following write-up, we will see the Universal Gates and Special Purpose Gates.

I am an electronics and communication graduate. I qualified GATE in the same domain in 2019. Due to the appetite for VLSI, I am going to join the Hong Kong University of Science and Technology for Masters in IC design this year. My interest in writing evoked during college time when I wrote technical essays for college fest. Apart from it, I am a part of a few local NGOs too.

Pingback: Modeling of Universal and Special Gates on Verilog - gossipfunda